DDR-SDRAM指的是雙倍速率同步動態(tài)隨機存儲器,是大多數(shù)處理器中使用的一種常用內(nèi)存類型�����。顧名思義�����,SDRAM表示同步���,并且依賴于時鐘信號���,以此為數(shù)據(jù)傳輸創(chuàng)建了預定義的周期。

? 安費諾連接器動態(tài)隨機存儲器(DRAM)是SDRAM內(nèi)存標準的前身��。DRAM于1970年推出���,但它是異步的���,即不受時鐘調節(jié)。隨著處理器速度變得越來越快���,DRAM無法跟上該速度��。這也促成了更有組織的SDRAM的發(fā)展�。

??第一代SDRAM是SDR-SDRAM�����,即單倍速率SDRAM�����,每個周期只能傳輸一個數(shù)據(jù)信號。為了提高數(shù)據(jù)傳輸?shù)乃俣群托?���,引入了DDR,它可以通過時鐘的前緣和下緣進行數(shù)據(jù)傳輸�,實現(xiàn)了SDRAM雙倍的速度。引入DDR之后�,內(nèi)存現(xiàn)在可以以更低的時鐘速率、更快的速度和更少的能量運行����。

? ?之后���,還引入了DDR2以滿足增強的速度要求�。它帶有一個額外的時鐘倍增器���,使數(shù)據(jù)傳輸速度提高了一倍�����,同時以相同的總線速度運行�����。隨后推出的DDR3 RAM具有集成4倍時鐘倍頻器��,可在不增加總線速度的情況下提高數(shù)據(jù)速度���。除了增強帶寬外���,DDR3消耗的功率比DDR2更少。

??于2014年上市的 DDR4 更在DDR3的基礎上提高了速度�。除此之外,此版本使用的電壓更低��,并且密度更高���。與DDR3的800~1600 MT/s傳輸速率相比���,DDR4的傳輸速率為2133~3200 MT/s。JEDEC已經(jīng)宣布即將推出下一代DDR5����,預計將在2020年發(fā)布。

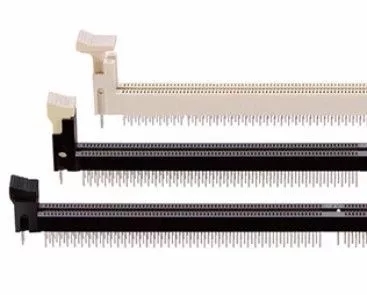

??Amphenol ICC利用DDR3內(nèi)存模塊插槽����、DDR4內(nèi)存模塊插槽���、DDR4超薄型內(nèi)存模塊插槽、DDR2 SO-DIMM內(nèi)存模塊插槽和DDR4 SO-DIMM內(nèi)存模塊插槽等連接器產(chǎn)品不斷推出解決方案來支持DDR SDRAM的發(fā)展���。

??我們也準備通過推出DDR5內(nèi)存模塊插槽(SMT)一起迎接即將到來的新技術��。我們還為DDR5產(chǎn)品提供標準和窄型鎖存器版本�����。窄型鎖存器版本可以增加氣流���,因為DIMM插槽預計會彼此相鄰放置。與此同時�,我們也很快將推出DDR5 SODIMM��。

DDR SDRAM解決方案

?